# APPLICATIONS HANDBOOK

Cypress Semiconductor is a trademark of Cypress Semiconductor Corporation. Cypress Semiconductor, 3901 North First St., San Jose, CA 95134 (408) 943–2600 Telex: 821032 CYPRESS SNJ UD, TWX: 910 997 0753, FAX: (408) 943–2741

IBM®. is a registered trademark of the International Business Machine Corporation. IBM PC®. is a registered trademark of the International Business Machine Corporation. SPARC<sup>TM</sup> is a trademark of Sun MicroSystems, Inc. Data I/O®. is a registered trademark of the Data I/O Corporation. PLD Test<sup>TM</sup> and ABEL<sup>TM</sup> are trademarks of the Data I/O Corporation. PC/XT<sup>TM</sup> is a trademark of the International Business Machine Corporation. STAG®. is a registered trademark of Stag Microsystems Ltd. Cypress PLD Toolkit<sup>TM</sup> is a trademark of Cypress Semiconductor Corporation.

## How to Use This Book

This book has been organized by product type, beginning with general articles that apply to all Cypress products. The individual applications notes follow, organized by product type. The order is: SRAMs, PROMs, EPLDs, Logic (including FIFOs and dual port RAMs), and RISC. Within each chapter, application notes are arranged in the order of part number. In cases where more than one Cypress product is used in the application, the article will be filed using the product which is the primary focus of the article.

Published August 1, 1989

<sup>©</sup> Cypress Semiconductor Corporation, 1989. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor Corporation product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life support systems where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life support system applications implies that the manufacturer assumes all risk of such use and in so doing indemnifies Cypress Semiconductor against all damages.

## **Table of Contents**

| General Information                       | Page Number |

|-------------------------------------------|-------------|

| System Design Considerations              |             |

| Power Characteristics of Cypress Products |             |

| Static RAMs                      | Page Number |

|----------------------------------|-------------|

| Tips for High-Speed Logic Design | 2-1         |

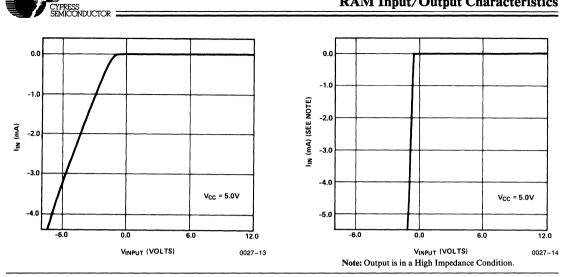

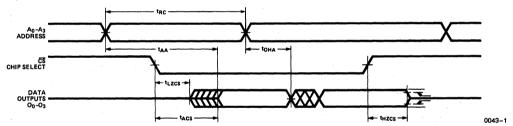

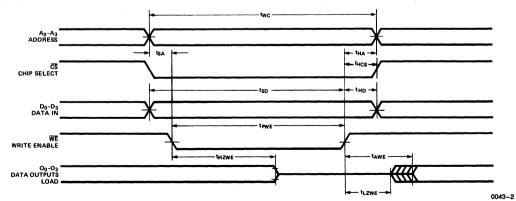

| RAM Input/Output Characteristics | 2-7         |

| 74F189 Application Brief         | 2-15        |

| PROMs                                                   | Page Number |

|---------------------------------------------------------|-------------|

| Introduction to Diagnostic PROMs                        |             |

| Pin-Out Compatibility Considerations of SRAMs and PROMs |             |

| EPLDs                                                  | Page Number |

|--------------------------------------------------------|-------------|

| Introduction to Programmable Logic                     | 4-1         |

| Programmable Logic Device Application Note             |             |

| PAL C16R6 Design Example: GRC Encoder/Decoder          |             |

| Using ABEL to Program the Cypress 22V10                |             |

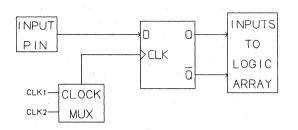

| Using ABEL to Program the CY7C330                      |             |

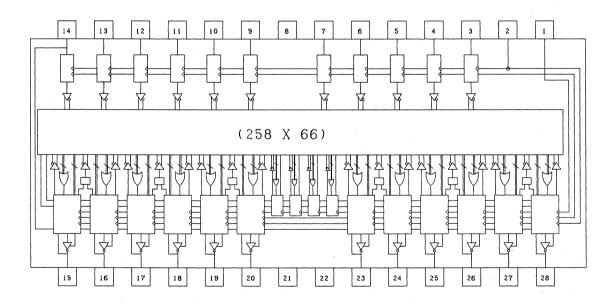

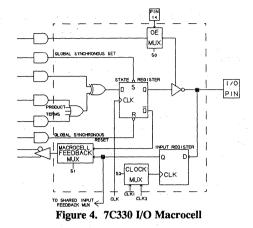

| CY7C330 66-MHz 28-Pin Synchronous EPLD                 |             |

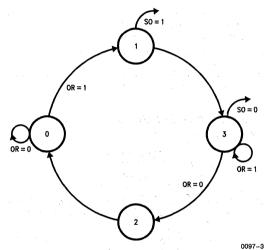

| CY7C330 State Machine Example: SCSI Host Adapter       |             |

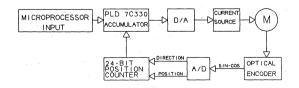

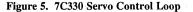

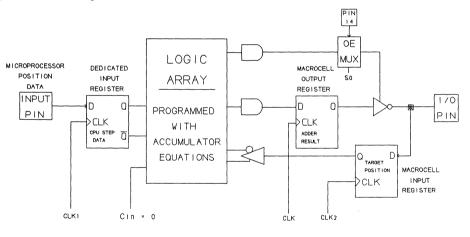

| Using the Cypress CY7C330 in Closed-Loop Servo Control |             |

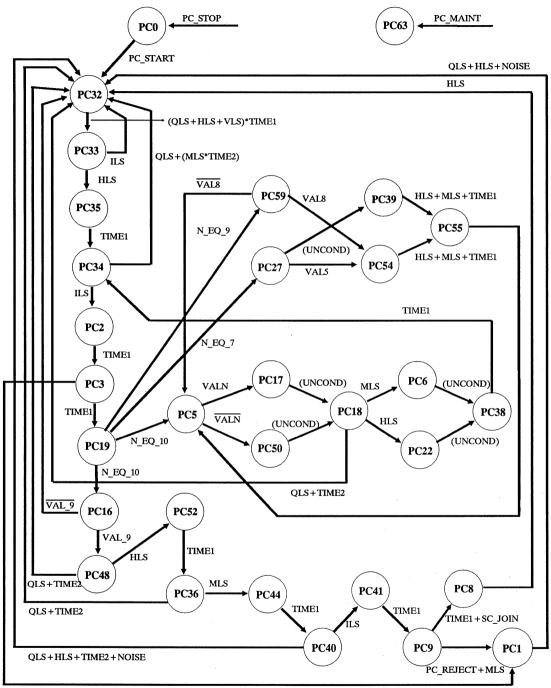

| FDDI Physical Connection Management Using the CY7C330  |             |

| CY7C331 Application Example: Asynchronous,             |             |

| Self-Timed VME Bus Requester                           | 4-131       |

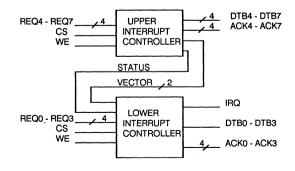

| Bus-Oriented Maskable Interrupt Controller             |             |

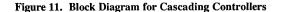

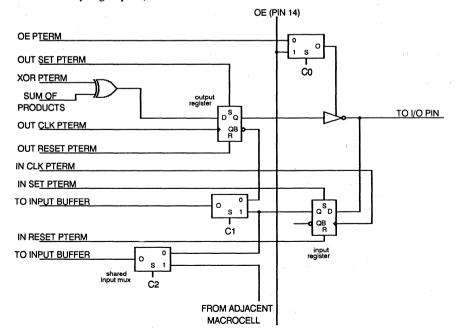

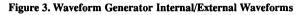

| Using the CY7C331 as a Waveform Generator              |             |

| Logic                                         | Page Number |

|-----------------------------------------------|-------------|

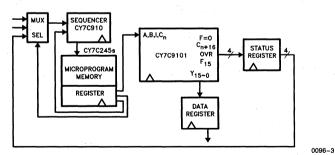

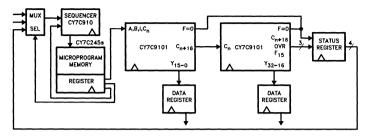

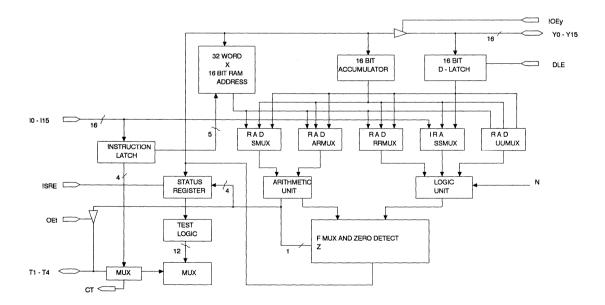

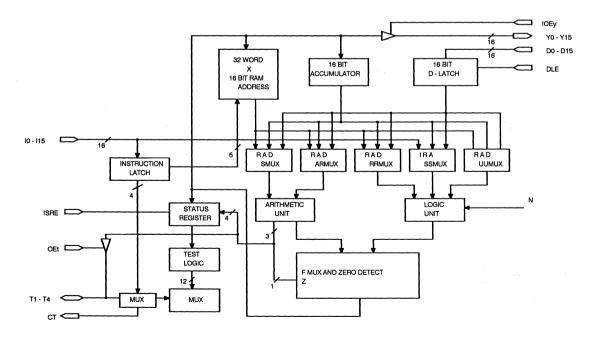

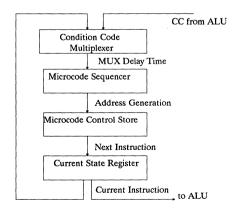

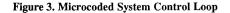

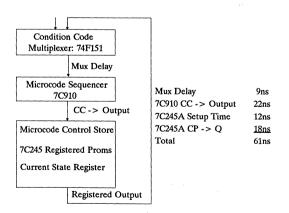

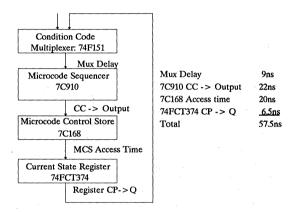

| Microcoded System Performance                 |             |

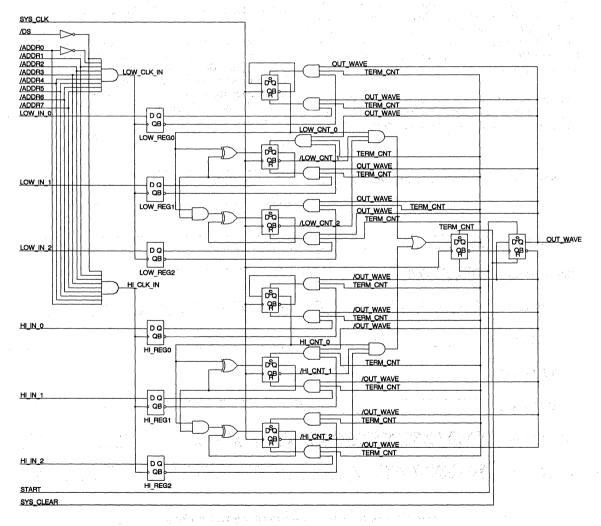

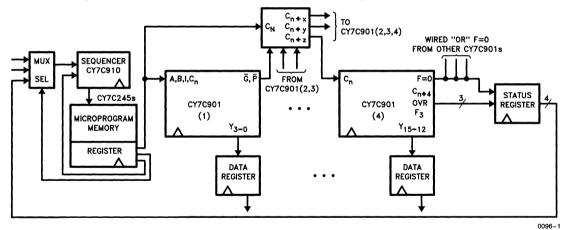

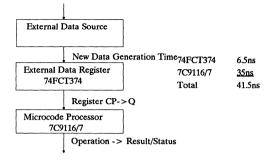

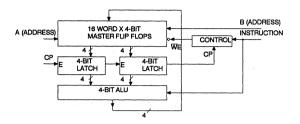

| Systems with CMOS 16-bit Microprogrammed ALUs | 5-5         |

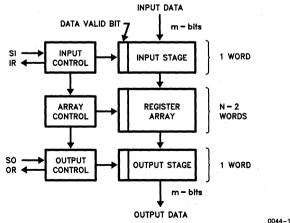

| Understanding FIFOs                           | 5-11        |

| Interfacing to the FIFO Application Brief     |             |

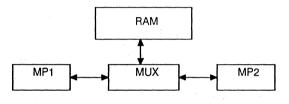

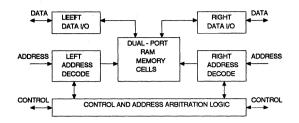

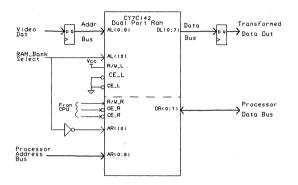

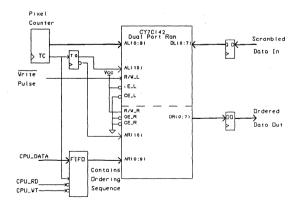

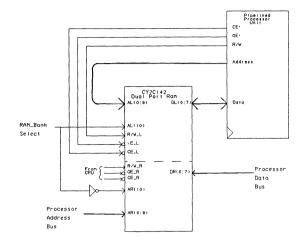

| Understanding Dual-Port RAMs                  |             |

| Using Dual Port RAMs Without Arbitration      | 5-41        |

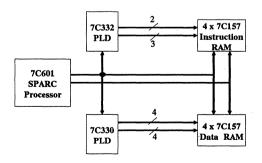

| RISC                                                 | Page Number |

|------------------------------------------------------|-------------|

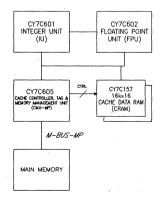

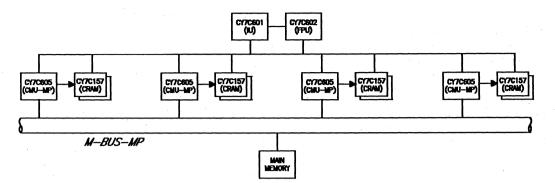

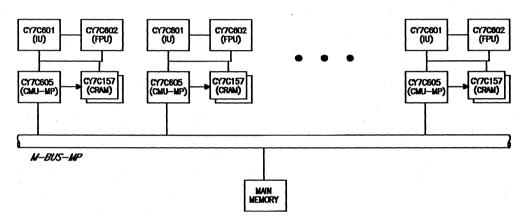

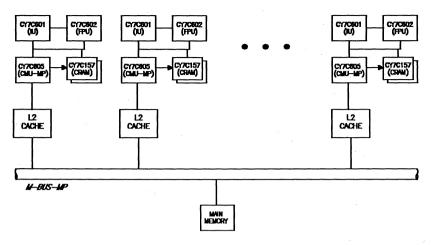

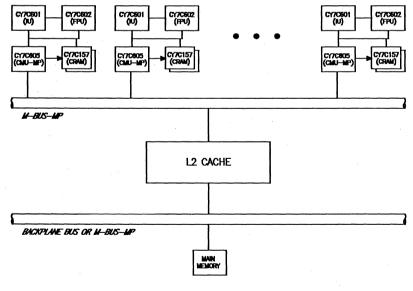

| Memory System Design for the CY7C601 SPARC Processor |             |

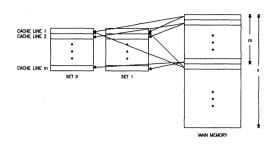

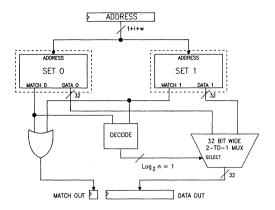

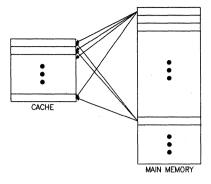

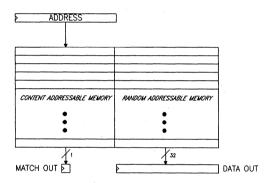

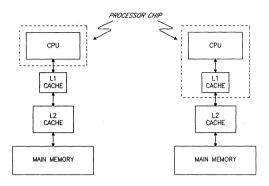

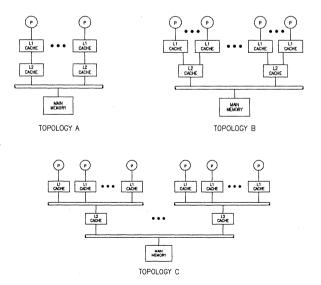

| Cache Memory Design                                  |             |

| SPARC as a Real-Time Controller                      |             |

| Using the CY7C330 as a Multi-channel Mbus Arbiter    |             |

| Index                                                | Index-1     |

|                                                      |             |

## **Section Contents**

| General Information                       | Page Number |

|-------------------------------------------|-------------|

| System Design Considerations              | 1-1         |

| Power Characteristics of Cypress Products |             |

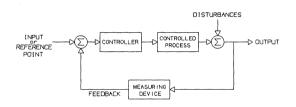

## Systems Design Considerations When Using Cypress CMOS Circuits

## Introduction

This document is intended to be a guide for the systems designer. Its purpose is to make him aware of the things to consider either when designing new systems using Cypress high performance CMOS integrated circuits or when Cypress products replace either bipolar or NMOS circuits in existing systems. The two major areas of concern are transmission line effects due to impedance mismatching between the source and load, and device input sensitivity.

#### **Design for Performance**

In order to achieve maximum performance when using Cypress CMOS integrated circuits, the systems designer must pay attention to the placement of the components on the Printed Circuit Board (PCB), the routing of the metal traces that interconnect the components, the layout and decoupling of the power distribution system on the PCB and, perhaps most important of all, the impedance matching of (some of) the traces (which, under certain conditions, must be analyzed as transmission lines) between the source and the loads. The most critical traces are those of clocks, write strobes (on SRAMS), and chip enables.

#### Issues of Concern When Cypress ICs Replace Either Bipolar or NMOS ICs

Cypress CMOS ICs have been designed to replace both bipolar ICs and NMOS products, and to achieve equal or better performance at one-third (or less) the power of the components they replace.

When high performance Cypress CMOS circuits replace either bipolar or NMOS circuits in existing sockets, the user must be aware of certain conditions, which may be present in the existing system, that could cause the Cypress ICs to behave in a manner different than expected. These conditions fall into two general categories; (1) device input sensitivity and, (2) sensitivity to reflected voltages.

### **Input Sensitivity**

High performance products, by definition, require less energy at their inputs to change state, than low or medium performance products.

Unlike a bipolar transistor, which is a current sensing device, a MOS transistor is a voltage sensing device. In fact, a MOS circuit design parameter called 'K' is analogous to

the gm of a vacuum tube, and is inversely proportional to the gate oxide thickness.

The thin gate oxides, which are required to achieve the desired performance, result in highly sensitive inputs that require very little energy. High frequency signals that bipolar devices would not respond to may be detected by CMOS products.

MOS transistors also have extremely high (5 to 10 million ohm) input impedances, which make their gate inputs analogous to the input of a high gain amplifier (or an RF antenna). In contrast, bipolar ICs have input impedances of  $1000\Omega$  or less, so they require much more energy to change state than MOS ICs. In fact, a Cypress IC requires less than 10 picojoules of energy to change state.

Therefore, when Cypress CMOS ICs replace either bipolar or NMOS ICs in existing systems, they may respond to pulses of energy that are present in the system that are not detected by the bipolar or NMOS products.

### **Reflected Voltages**

Cypress CMOS ICs have very high input impedances and, to achieve TTL compatibility and to drive capacitive loads, low output impedances. The impedance mismatch, due to low impedance outputs driving high impedance inputs may, under certain conditions, cause unwanted voltage reflections and ringing, which could result in less than optimum system operation.

When the impedance mismatch is very large, a nearly equal and opposite negative pulse is reflected back from the load to the source when the (electrical) length of the line (PCB trace) is greater than

$$\ell = \frac{T_R}{2 T_{pd}} (ns) (ns/ft.)$$

where  $T_{R}$  is the rise time of the signal at the source and  $T_{pd}$  is the one-way propagation delay of the line per unit length.

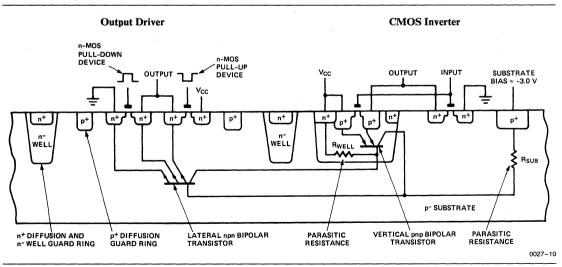

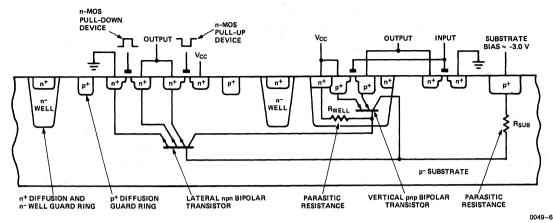

The input clamping diodes that bipolar logic "IC families" (e.g., TTL, LS, ALS, FAST) all have are inherent in the fabrication process. The p-substrate is usually grounded and n wells are used for the NPN transistors and p type resistors. The wells are reverse biased by connecting them to the  $V_{CC}$  supply. As a result, a PN junction diode is formed between every input pin (cathode or n material)

## Introduction (Continued)

and the substrate (anode or p-material). When a negative voltage occurs at an input pin, either due to lead inductance or to a voltage reflection, the diode is forward biased, turns on, and clamps the input pin to a Vf below ground (approximately -0.8V).

As circuit performance improved, the output rise and fall times of the bipolar circuits decreased to the point where voltage reflections began to occur (even for short traces) when there was an impedance mismatch between the line and the load. Most users, however, were unaware of these reflections because they were suppressed by the clamping action of the diodes.

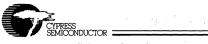

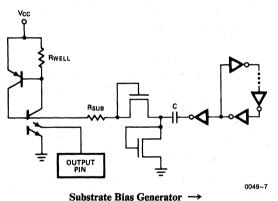

Conventional CMOS processing results in PN junction diodes. However, they adversely affect the ESD (Electrostatic Discharge) protection circuitry at each input pin and cause an increased susceptibility to latchup. To eliminate this, a substrate bias generator is used.

Voltage reflections should be eliminated by using impedance matching techniques and crosstalk should be reduced by careful PCB layout.

#### Crosstalk

The rise and fall times of the waveforms generated by the output circuits are 2 to 4 ns between levels of 0.4V and 4V. The fast transition times and the large voltage swings could cause capacitive and inductive coupling (crosstalk) between signals if insufficient attention is paid to PCB layout. Crosstalk is reduced by avoiding running PCB traces parallel to each other. If this is not possible, ground traces should be run between signal traces. In synchronous systems, the worst time for the crosstalk to occur is during the clock edge with which the data is sampled. In most systems it is sufficient to isolate the clock and other data strobe lines so that they do not cause coupling to the data lines.

## The Theory of Transmission Lines

A connection (trace) on a PCB should be considered as a transmission line if the wavelength of the applied frequency is short compared to the line length. If the wavelength of the applied frequency is long compared to the length of the line, conventional circuit analysis can be used.

In practice, transmission lines on PCBs are designed to be as nearly lossless as possible. As a result, the mathematics required for their analysis, compared to a lossy (resistive) line can be simplified.

Ideally, all signals between ICs travel over constant-impedance transmission lines that are terminated in their characteristic impedances at the load. In practice this ideal situation is seldom achieved for a variety of reasons.

Perhaps the most basic reason is that the characteristic impedances of all real transmission lines are not constants, but present different impedances depending upon the frequency of the applied signal. For "classical" transmission lines driven by a single frequency signal source the characteristic impedance is "more constant" than when the transmission line is driven by a square wave or a pulse.

A square wave is composed of an infinite set (Fourier series expansion) of discrete frequency components, i.e., fundamental plus odd harmonics of decreasing amplitudes. When the square wave is propagated down a transmission line the higher frequencies are attenuated more than the lower frequencies and, due to dispersion, all of the frequencies do not travel at the same speed.

Dispersion indicates the dependance of phase velocity upon the applied frequency. (Ref. 1, pg. 192). The result is that the square wave is distorted when all of the frequency components are added together at the load.

A secondary reason why practical transmission lines are not ideal is that they frequently (of necessity) have multiple loads. The loads may be distributed along the line at regular (or irregular) intervals or they may be lumped together (as close as practical) at the end of the line. The signal-line reflections and ringing caused by impedance mismatches, nonuniform transmission line impedances, inductive leads, and non-ideal resistors could compromise the dynamic system noise margins and cause inadvertent switching.

One of the system design objectives is to analyze the critical signal paths and design the interconnections such that adequate system noise margins are maintained. There will always be signal overshoot and undershoot. The objective is to accurately predict them and to keep them within acceptable limits.

### The Ideal (Lossless) Transmission Line

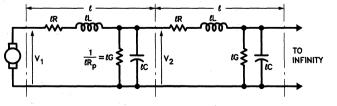

An equivalent circuit for a transmission line is presented in *Figure 2.1.* It consists of subsections of series resistance (R) and inductance (L) and parallel capacitance (C) and shunt admittance (G) (or parallel resistance, Rp). For clarity and consistency these parameters will be defined per unit length. The value of the parameter (R, L, C, Rp) must be multiplied by the length of the subsection,  $\ell$ , to find the total value. The line is assumed to be infinitely long.

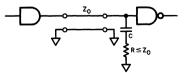

If the line of Figure 2.1 is assumed to lossless (R = 0,  $R_P = infinity$ ) Figure 2.1 is reduced to Figure 2.2.

0099-1

Figure 2.1. Transmission Line Model

Figure 2.2. Ideal Transmission Line Model

0099-2

## **Input or Characteristic Impedance**

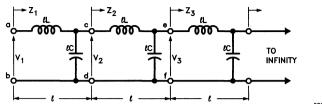

We shall now calculate the characteristic impedance (AC impedance or surge impedance) looking into terminals a-b of Figure 2.2.

Let the input impedance looking into terminals a-b be Z1, that looking into terminals c-d be Z2, that looking into terminals e-f be Z3, etc. The input impedance, Z1, looking into terminals a-b is the series impedance of the first inductor  $(\ell L)$  in series with the parallel combination of Z2 and the impedance of the capacitor ( $\ell$  C).

From AC theory:

$$XL = j\omega \ell L$$

Where XL is the inductive reactance.

$$XC = \frac{1}{j\omega \ell C}$$

Where XC is the capacitive reactance.  $\mathbf{Z1}$

Then

$$= XL + \frac{Z2 XC}{Z2 + XC}$$

(2-1)

If the line is "reasonably" long Z1 = Z2 = Z3. Substituting Z1 = Z2 into equation 2-1 yields;

$$Z1 = XL + \frac{Z1 XC}{Z1 + XC}.$$

Or,  $Z1^2 - Z1 XL - XC XL = 0$  (2-2)

Substituting the expressions for XC and XL yields:

$$Z1^2 - j\omega \ell L = \frac{L}{C}$$

(2-3)

Equation 2-3 contains a complex component that is frequency dependent. It can be eliminated by allowing  $\ell$  to become very small and by recognizing that the ratio L/C is constant and independent of  $\ell$  or  $\omega$ .

$$Z1 = \sqrt{\frac{L}{C}}$$

(2-4)

The AC input impedance of a purely reactive, uniform, lossless line is a resistance. This is true for AC or DC excitation.

#### **Propagation Velocity and Propagation Delay**

The propagation velocity (or phase velocity) of a sinusoid traveling on an ideal line (Ref. 1, pg. 33) is:

$$\alpha = \frac{1}{\sqrt{\mathrm{LC}}}.$$

The propagation delay for a lossless line is the reciprocal of the propagation velocity.

$$T_{pd} = \sqrt{LC}$$

(2-5)

= 71 C

where L and C are the intrinsic line inductance and capacitance per unit length.

If additional stubs or loads are added to the line the propagation delay will increase by the factor (Ref. 2, pg. 129).

$$\sqrt{1+\frac{C_D}{C}}$$

Where  $C_{D} = load$  capacitance.

Therefore, the propagation delay, TPD', of a loaded line is:

$$T_{PD}' = T_{PD} \sqrt{1 + \frac{C_D}{C}}.$$

(2-6)

The characteristic impedance of a capacitively loaded line is decreased by the same factor that the propagation delay is increased.

$$Z1' = \frac{Z1}{\sqrt{1 + \frac{C_D}{C}}}$$

(2-7)

## **Reflection Coefficients**

The third attribute of the ideal transmission line: reflection coefficients, are not actually a line characteristic. The line is treated as a circuit component (which it is) and reflection coefficients are defined that measure the impedance mismatches between the line and its source and the line and its load. The reason for defining the reflection coefficients will become apparent later when it will be shown that if the impedance mismatch is sufficiently large, either a negative voltage or a positive voltage may be reflected back from the load to the source, where it may either add to or subtract from the original signal. If the impedance of the source is mismatched to the line impedance it may also cause a voltage reflection, which in turn will be reflected back to the load. Therefore, two reflection coefficients will be defined.

For classical transmission lines driven by a single frequency source the impedance mismatches cause standing waves. When pulses are transmitted and the output impedance of the source changes depending upon whether a LOW to HIGH or a HIGH to LOW transition occurs, the analysis is further complicated. Classical transmission analysis,

where pulses are represented by complex variables with exponentials, could be used to calculate the voltages at the source and the load after several back and forth reflections. However, these complex equations tend to obscure what is physically happening.

#### **Energy Considerations**

Consider next, driving the ideal transmission line from a source capable of generating digital pulses and analyze the behavior of the line under various driving and loading conditions.

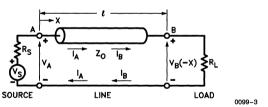

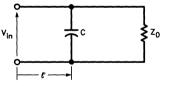

The circuit to be analyzed is illustrated in Figure 2.3. The ideal transmission line of length  $\ell$  is being driven by a digital source of internal resistance Rs and loaded with a resistive load of RL. The characteristic impedance of the line appears as a pure resistance,  $Z_O = \sqrt{L/C}$  to any excitation.

The ideal case is when  $R_S = Z_O = RL$ . The maximum energy transfer from source to load occurs under this condition, and there are no reflections. One half the energy is dissipated in the source resistance, Rs, and the other half is dissipated in the load resistance, RL, (the line is lossless).

If the load resistor is greater (larger) than the characteristic impedance of the line there will be extra energy available at the load, which will be reflected back to the source. This is called the underdamped condition, because the load underuses the energy available. If the load resistor is smaller than the line impedance the load will attempt to dissipate more energy than is available. Since this is not possible, a reflection will occur that is a signal to the source to send more energy. This is called the overdamped condition. Both of these cases will cause negative traveling waves, which would cause standing waves if the excitation were sinusoidal. The condition  $Z_0 = RL$  is called critically damped.

It should be intuitively obvious to the reader that the "safest" termination condition, from a systems design viewpoint, is the slightly overdamped condition. No energy is reflected back to the source.

### **Derivation of the Line Voltage for Step Function Excitation**

The procedure is to apply a step function to the ideal line and to analyze the behavior of the line under various loading conditions. The following section will analyze pulses, reflections from various terminations, and the effects of rise times on the waveforms.

The step function response is important because any pulse can be represented by the superposition of a positive step function and a negative step function, delayed in time with respect to each other. By proper superposition the response of any line and load to any width pulse can be predicted. The principle of superposition applies to all linear systems.

According to theory, the risetime of the signal driven by the source is not affected by the characteristics of the line. This has been substantiated in practice by using a special coaxially constructed reed delay that delivered a pulse of 18 amperes into 50 $\Omega$  with a risetime of 0.070 ns (70 ps). (Ref. 1, pg. 162).

The equation representing the voltage waveform going down the line (Figure 2.3) as a function of distance and time is:

$$VL(X, t) = VA(t) U(t - X tpd)$$

for  $t < T_0$  (2-8)

Where:

$$VA(t) =$$

$V_{S}(t)\left(\frac{Z_{O}}{Z_{O}+R_{s}}\right)$ (2-9)VA(t)

VA = the voltage at point A

X = the voltage at a point X on the line

$\ell$  = the total line length

$t_{pd}$  = the propagation delay of the line in ns/ft.

$T_O = \ell t_{pd}$ , or the one-way line propagation delay

U(t) = a unit step function occurring at X = 0, and

$V_{S}(t) =$  the source voltage

When the incident voltage reaches the end of the line a reflected voltage, VL', will occur if RL is not equal to Zo. The reflection coefficient at the load,  $\rho L$ , can be obtained by applying Ohm's Law.

The voltage at the load is VL + VL', which must be equal to  $(I_L + I_L')RL$ . But  $I_L = VL/Z_O$  and  $I_L' = -VL'/Z_O$ (the minus sign is due to I<sub>1</sub> being negative. i.e., it is opposite to the current due to VL.)

Therefore.

$$\mathbf{VB} = \mathbf{VL} + \mathbf{VL'} = \left(\frac{\mathbf{VL}}{\mathbf{Z}_{O}} - \frac{\mathbf{VL'}}{\mathbf{Z}_{O}}\right) \mathbf{RL} \quad (2-10)$$

By definition:

$$\rho L = \frac{\text{reflected voltage}}{\text{incident voltage}} = \frac{VL'}{VL}$$

Solving for VL'/VL in equation 2-10 and substituting in the equation for  $\rho L$  yields:

$$\rho L = \frac{RL - Z_0}{RL + Z_0}.$$

(2-11)

The reflection coefficient at the source is:

$$\rho \mathbf{S} = \frac{\mathbf{R}_{\mathbf{S}} - \mathbf{Z}_{\mathbf{O}}}{\mathbf{R}\mathbf{L} + \mathbf{Z}_{\mathbf{O}}}.$$

(2-12)

Re-arranging equation 2-10 yields:

$$\mathbf{VB} = \mathbf{VL} + \mathbf{VL'} = \left(1 + \frac{\mathbf{VL'}}{\mathbf{VL}}\right)\mathbf{VL} = (1 + \rho\mathbf{L})\mathbf{VL} \quad (2-13)$$

Equation 2-13 describes the voltage at the load (VB) as the sum of an incident voltage (VL) and a reflected voltage (pL VL) at time  $t = T_0$ . When  $RL = Z_0$  no voltage is reflected. When  $RL < Z_0$  the reflection coefficient at the load is negative, so the reflected voltage subtracts from the incident voltage, giving the load voltage. When  $RL > Z_O$  the reflection coefficient is positive, so the reflected voltage adds to the incident voltage, again giving the load voltage. Note that the reflected voltage at the load has been defined as positive when traveling toward the source. This means that the corresponding current must be negative, subtracting from the current driven by the source, which it does.

This "piecewise" analysis is cumbersome and can be tedious. However, it does provide an insight into what is physi-

cally happening and demonstrates that a complex problem can be solved by dividing it into a series of simpler problems. Also, the mathematics are simple if the exponentials, which provide phase information in the classical transmission line equations, are eliminated. One must provide the "bookkeeping" to combine the reflections at the proper time. This is quite straightforward, since a pulse travels with a constant velocity along an ideal or low loss line and the time delay between reflected pulses can be predicted.

The rules to keep in mind are that at any point and instant of time the voltage or the current is the algebraic sum of the waves traveling in the positive X and the negative X directions. For example, two voltage waves of the same polarity and equal amplitudes, traveling in opposite directions, at a given point and time will add together to yield a voltage of twice the amplitude of the individual wave. The same reasoning applies to points of termination and discontinuities on the line. The total voltage or current is the algebraic sum of all of the incident and reflected waves. Polarities must be observed. A positive voltage reflection results in a negative current reflection and vice versa.

Before considering reflections at the source, due to impedance mismatches between the source impedance and the line impedance, the behavior of the ideal line with various loads will be analyzed when it is driven by a step function.

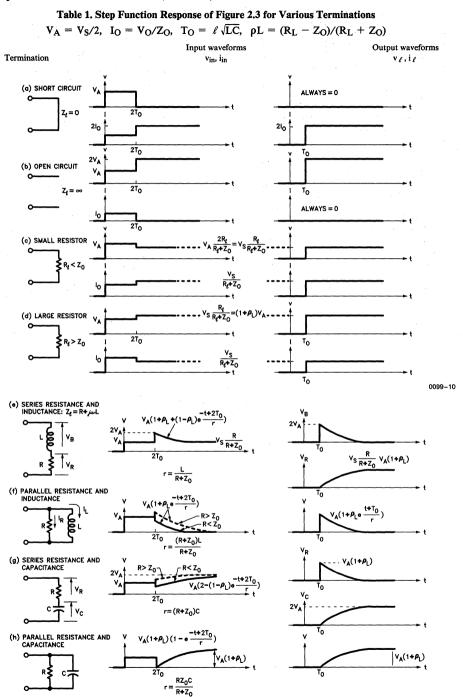

## Step Function Response of the Ideal Line for Various Loads

The voltage and current waveforms at point A (line input, Figure 2.3) and point B (the load) for various loads are presented in Table 1. They have been reproduced from Table 5.1, pages 158, 159 of Reference 1. Note that  $R_S = Z_O$  and that VA at t = 0 is equal to V<sub>S</sub>/2, which means that there is no impedance mismatch between the source and the line, so there will be no reflection from the source at  $t = 2 T_O$ .

To is the one way propation of the line.

The time domain response of the reactive loads are obtained by applying a step function to the LaPlace transform of the load and then taking the inverse transform.

Note that the reflection coefficient at the load is not the total reflection coefficient (a complex number) but represents only the real part of the load. The reason for doing this is to eliminate the complex (j $\omega$ t) terms because we are performing the bookkeeping involving the phase relationships, which are performed by them in classical transmission line analysis.

Also note that for the open circuit condition, Table 1 (b), ZL = infinity, so that  $\rho L = +1$ . The voltage is reflected back from the load to the source (at amplitude  $V_O = V_S/2$ ), so that at time = 2 T<sub>O</sub> it adds to the original voltage,  $V_O = V_S/2$  to give a value of 2  $V_O = V_S$ . During the time the voltage wave is traveling down to and back from the load a current of  $I_O = V_O/Z_O = V_S/2 Z_O$  exists. This current charges up the distributed line capacitance to the value  $V_S$ , at which time it stops.

Direction of Travel VA, IA  $\rightarrow +X$ VB, IB  $\leftarrow -X$

Figure 2.3. Ideal Transmission Line Loaded and Driven

0099-11

The waveforms at the source and load for (g) and (h) are of particular interest because (g) represents a series RC termination that dissipates no DC power and can be used to terminate a transmission line in its characteristic impedance at the input to a Cypress IC. The equivalent circuit of the input to a Cypress IC is represented by (h). The addition of (g) and (h) then models a Cypress IC driven by a transmission line terminated in its characteristic impedance when the values of R and C are properly chosen.

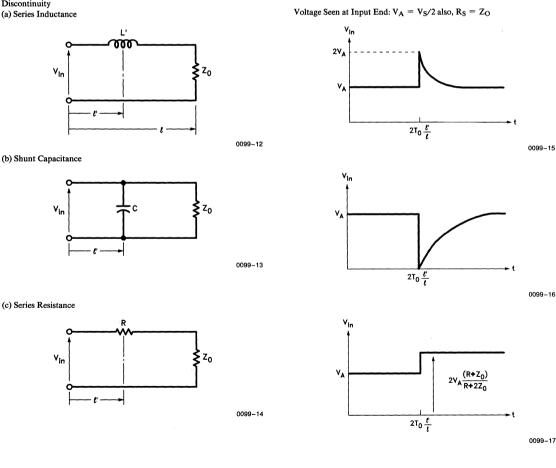

### **Reflections Due to Discontinuities**

Table 2 illustrates three types of common discontinuities found on transmission lines. When a discontinuity occurs at a point on the line it causes a reflection and some energy is directed back to the source. The amount of energy reflected back is determined by the reflection coefficient at that point. Discontinuities are usually small (by design), so most of the energy is transmitted to the load.

## **Pulse Response of the Ideal Transmission Line**

Consider next the behavior of the ideal transmission line when driven by a pulse whose width is short compared to the electrical length of the line. In other words, when the width of the pulse is less than the one-way propagation delay time, To, of the line.

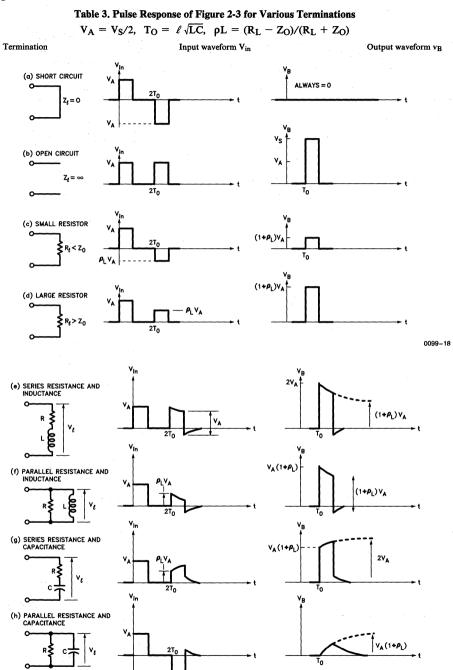

The voltage waveforms at point A (line input, Figure 2.3) and point B (the load) for various loads are presented in Table 3. They have been reproduced from Table 5.2, pages 160, 161 of Reference 1. Note that  $R_S = Z_O$  and that VA at t = 0 is equal to V<sub>S</sub>/2, which means that there is no impedance mismatch between the source and the line, so there will be no reflection from the source at  $t = 2 T_{O}$ .

#### Table 2. Reflections from Discontinuities with an Applied Step Function

Discontinuity

(b) Shunt Capacitance

(c) Series Resistance

## Pulse Response of the Ideal Transmission Line (Continued)

0099-19

-V.

## **Finite Rise Time Effects**

Now consider the effects of step functions with finite rise times driving the ideal transmission line.

If TR is sufficiently fast, the voltage at the load will change in discrete steps. The amplitude of the steps is determined by the impedance mismatch and the width of the steps is determined by the two-way propagation delay of the line.

As the risetime becomes slower and the line shorter (smaller  $T_O$ ), or both, the result converges to the familiar RC time constant, where C is the static capacitance. All devices should be treated as transmission lines for transient analysis when an ideal step function is applied. However, as the rise time becomes larger (slower) and the traces shorter (or both) the transmission line analysis reduces to conventional AC circuit analysis.

### **Reflections from Small Discontinuities**

Table 4 shows a pulse with a linear rise time and rounded edges driving the transmission line of Table 2 (a), (b). The expressions for  $V_r$  are derived on pages 171 and 172 of Reference 1. The reflection caused by the small series inductance is useful for calculating the value of the inductor, L', but little else.

## Table 4. Reflections from Small Discontinuities with Finite Rise Time Pulse

(a) Applied Pulse from Generator

(b) Reflection from Small Series Inductor L'

(c) Reflection from Small Shunt Capacitor C'

The reflection caused by the small shunt capacitor is more interesting because if it is sufficiently large it could cause a device connected to the transmission line to see a logic ZERO instead of a logic ONE.

### The Effect of Rise Time on Waveforms

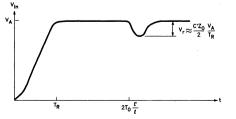

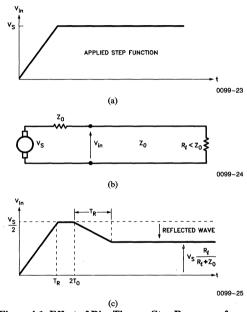

Next, consider the ideal line terminated in a resistance less than its characteristic impedance and driven by a step function with a linear rise time. The stimulus, the circuit, and the response are illustrated in Figures 4.1 (a), (b) and (c), respectively. Once again, note that the source resistance is equal to the line characteristic impedance, so there are no reflections from the source.

## Figure 4.1. Effect of Rise Time on Step Response of Mismatched Line with $R_{\ell} < Z_{O}$

The resulting waveforms are similar to those of Table 1 (c) as modified as shown in *Figure 4.1 (c)*. The final value of the waveform must be the same as before (Table 1 (c)).

The resultant wave at the line input (V<sub>in</sub>) is easily obtained by superposition of the applied wave and the reflected wave at the proper time. In *Figure 4.1* the rise time of the step function is less than the (two-way) propagation delay of the line so the input wave reaches its final value, V<sub>S</sub>/2. At t =2 T<sub>O</sub> the reflected wave arrives back at the source and subtracts from the applied step function.

The cases where the step function rise time is equal to twice the propagation delay and greater than the propagation delay are illustrated in *Figure 4.2 (a)* and *(b)*, respectively.

0099-22

0000-21

## Finite Rise Time Effects (Continued)

(b)  $T_R > 2 T_O$ Figure 4.2. Effects of Rise Time on Step Response for  $R_{\ell} < Z_{O}$ : (a)  $T_{R} = 2 T_{O}$ ; (b)  $T_{R} > 2 T_{O}$

### **Multiple Reflections and Effective Time** Constant

We will now consider the case of an ideal transmission line with multiple reflections causes by improper terminations at both ends of the line. The circuit and waveforms are illustrated in Figure 4.3. The reflection coefficients at the source and the load are both negative. i.e., the source resistance and the load resistance are both less than the line characteristic impedance. Refer to equations 2-11 and 2-12.

When the switch is initially closed, a step function of am-

plitude  $V_O = V_{in} = \frac{V_S Z_O}{R_S + Z_O}$  appears on the line and

travels toward the load. A one-way propagation delay time later, T<sub>0</sub>, the wave is reflected back with an amplitude of ρL V<sub>O</sub>.

This first reflected wave then travels back to the source and at time  $t = 2 T_0$  it reaches the input end of the line. At this time the first reflection at the source occurs and a wave of amplitude  $\rho S (\rho L V_0)$  is reflected back to the load. At time  $t = 3 T_0$  this wave is again reflected from the load back to the source with amplitude  $\rho L \rho S (\rho L V_0) = \rho S$  $\rho L^2 V_0$ . This back and forth reflection process continues until the amplitudes of the reflections become so small that they cannot be observed, at which time the circuit is said to be in a quiescent state.

#### **Effective Time Constant**

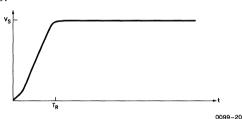

From an examination of *Figure 4.3* it is reasonable that if the voltage reflections occur in small increments that are of short durations the resultant waveform will approximate an exponential function, as indicated by the dashed line in Figure 4.3 (b). The smaller and narrower the steps become, the more closely the waveform will approach an exponential.

Figure 4.3. Step Function Applied to Line Mismatched on both ends; waveforms shown for negative values of  $\rho_S$  and  $\rho_\ell$ .

The mathematical derivation is presented on pages 178 and 179 of Reference 1. The time constant is shown to be:

$$K = -\frac{2 T_{O}}{1 - \rho S \rho L}$$

(4-1)

So that the resultant waveform can be approximated by;

$$V(t) = V_{O} \epsilon \left(\frac{t}{K}\right)$$

(4-2)

In order for equation 4-2 to be accurate pL and ps must be reasonably large (approaching  $\pm 1$ ) so that the incremental steps are small. The product  $\rho S \rho L$  is a positive number, less than one, so the time constant is a negative number, which indicates that the exponential decreases with time. This is usually the case in transient circuits.

Both reflection coefficients must also have the same sign in order to yield a continually decreasing (or increasing) waveform. Opposite signs will give oscillatory behavior that cannot be represented by an exponential function.

## Finite Rise Time Effects (Continued)

## The Transition from Transmission Line to Circuit Analysis

When a transmission line is terminated in its characteristic impedance it behaves like a resistor and it usually does not matter if transmission line or circuit analysis is used; provided that the propagation delays are taken into account.

Consider the case of a short-circuited transmission line driven by a step function with a source impedance unequal to the characteristic line impedance. The general case is shown in Figure 4.3 (a). For RL = 0 the reflection coefficients are;

$$\rho S = \frac{Z_S - Z_O}{Z_S + Z_O} \rho L = -1.$$

The approximate time constant is;

$$-k = \frac{2 T_{O}}{1 - \rho S \rho L} = \frac{2 T_{O}}{1 + \rho S} = \frac{T_{O} (Z_{S} + Z_{O})}{Z_{S}}, \text{ or}$$

$$-k = T_{O} + \frac{T_{O} Z_{O}}{Z_{S}}$$

(4-3)

Recall that  $T_O = \ell \sqrt{LC}$  (one-way delay)

and  $Z_O = \sqrt{\frac{L}{C}}$ , where  $\ell$  is the physical length of the line and L and C are the per-unit-length parameters.

Substitution of these into equation 4-3 yields

$$-k = T_{O} + \ell \frac{L}{Z_{S}}$$

It is necessary to have Z<sub>S</sub> smaller than Z<sub>O</sub>.

Thus the reflection coefficients have the same sign in order to give exponential behavior. Opposite signs give oscillatory behavior.

If  $Z_S \ll Z_O$ , the exponential approximation becomes more accurate. If  $Z_S$  is very small compared to  $Z_O$ , then  $T_O$  is negligible compared to  $\ell$  L/Z<sub>O</sub>, so that equation 4-5 reduces to;

$$\mathbf{k} = -\ell \frac{\mathbf{L}}{\mathbf{Z}_{\mathbf{S}}}.$$

But  $\ell$  L is the total loop inductance and Z<sub>S</sub> is the total series impedance of the circuit. The time constant is then;

$$k = \frac{L'}{R_S}.$$

This is the same time constant that would have been obtained by a circuit analysis approach if the line were considered a series combination of L' and  $R_S$ .

By open-circuiting the line and performing a similar analysis it can be shown that a RC time constant results.

## **Types of Transmission Lines**

The types of transmission lines are: Coaxial cable Twisted pair Wire over ground Microstrip lines Strip lines

### **Coaxial Cable**

Coaxial cable offers many advantages for distributing high frequency signals. The well defined and uniform characteristic impedance permits easy matching. The ground shield on the cable reduces crosstalk and the low attenuation at high frequencies make it ideal for transmitting the fast rise and fall time signals generated by Cypress CMOS integrated circuits. However, because of its high cost, coaxial cable is usually restricted to applications where there are no other alternatives. These are usually clock distribution lines on PCBs or backplanes.

#### **Characteristic Impedance**

Coaxial cables have characteristic impedances of 50, 75, 93, or 150 ohms. Special cables can be made with other impedances, but these are the most common.

#### **Propagation Delay**

The propagation delay is very low. It may be computed using the formula;

$$T_{pd} = 1.017 \sqrt{e_r} \text{ ns/ft.}$$

(5-1)

where  $e_r$  is the relative dielectric constant and depends upon the dielectric material used. For solid teflon and polyethylene it is 2.3. The propagation delay is 1.54 ns per foot. For maximum propagation velocity, coaxial cables with dielectric styrofoam or polystyrene beads in air may be used. Many of these cables have high characteristic impedances and are slowed considerably when capacitively loaded.

#### **Twisted Pair**

Twisted pairs can be made from standard wire (AWG 24-28) twisted about 30 turns per foot. Typical characteristic impedance is  $110\Omega$ . Because the propagation delay is directly proportional to the characteristic impedance (equation 2-5) the propagation delay will be approximately twice that of coaxial cable. Twisted pairs are used for backplane wiring and for breadboarding.

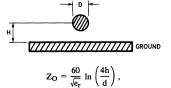

#### Wire Over Ground

Figure 5.1 shows a wire over ground. The wire over ground is used for breadboarding and for backplane wiring. The characteristic impedance is approximately  $120\Omega$  and may vary as much as  $\pm 40\%$ , depending upon the distance from the groundplane, the proximity of other wires, and the configuration of the ground.

0099-32

Figure 5.1. Wire Over Ground

## Types of Transmission Lines (Continued)

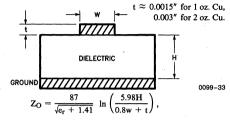

#### **Microstrip Lines**

A microstrip line (Figure 5.2) is a strip conductor (signal line) on a PCB separated from a ground plane by a dielectric. If the thickness and width of the line, and the distance from the ground plane are controlled, the characteristic impedance of the line can be predicted with a tolerance of  $\pm 5\%$ .

where:

er = relative dielectric constant of the board material (about 5 for G-10 fiber-glass epoxy boards),

w, h, t, = dimensions indicated.

Figure 5.2. Microstrip Line

The formula of *Figure 5.2* has proven to be very accurate for ratios of width to height between 0.1 and 3.0 and for dielectric constants between 1 and 15.

The inductance per foot for microstrip lines is;

$$\mathbf{L} = \mathbf{Z}_{\mathbf{O}}^2 \, \mathbf{C}_{\mathbf{O}} \tag{5-2}$$

where  $Z_0$  = characteristic impedance,

$C_0$  = capacitance per foot.

The propagation delay of a microstrip line is;

$$T_{pd} = 1.017 \sqrt{0.45 e_r} + 0.67$$

ns per foot. (5-3)

Note that the propagation delay is dependent only upon the dielectric constant and is not a function of the line width or spacing. For G-10 fiber-glass epoxy PCBs (dielectric constant of 5), the propagation delay is 1.74 ns per foot.

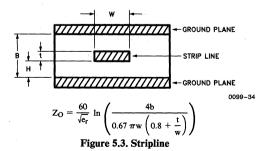

#### Strip Line

A strip line consists of a copper strip centered in a dielectric between two conducting planes (Figure 5.3). If the thickness and width of the line, the dielectric constant, and the distance between ground planes are all controlled, the tolerance of the characteristic impedance will be within  $\pm 5\%$ . The equation of Figure 5.3 is accurate for W/(b-t) < 0.35 and t/b < 0.25.

The inductance per foot is given by the formula;

$$L_{O} = Z_{O}^{2} C_{O}$$

.

The propagation delay of the line is given by the formula;

$$T_{pd} = 1.017 \sqrt{e_r} \text{ ns per foot.}$$

(5-4)

For G-10 fiber-glass epoxy boards the propagation delay is 2.27 ns per foot. The propagation delay is not a function of line width or spacing.

## **Power Distribution**

#### **Instantaneous Current**

In order to realize the fast rise and fall times that Cypress CMOS integrated circuits are capable of achieving, the power distribution system must be capable of supplying the instantaneous current required when the device outputs switch from LOW to HIGH.

The energy is stored as charge on the local decoupling capacitors. It is standard practice to use one decoupling capacitor for each IC that drives a transmission line and to use one for every three devices that do not.

The value of the decoupling capacitor is determined by estimating the instantaneous current required when all the outputs of the IC switch from LOW to HIGH, assuming a reasonable "droop" of the voltage on the capacitor.

#### Calculations

The charge stored on the local decoupling capacitor of *Figure 6.1* is Q = C V. Differentiating yields;

$$i(t) = \frac{dQ}{dt} = C \frac{dV}{dt}.$$

(6-1)

The characteristic impedance of a typical transmission line is  $50\Omega$ . Heavily (capacitively) loaded lines will have lower characteristic impedances (equation 2-7).

#### Figure 6.1. Local Decoupling Capacitor

Next, assume that the IC is an eight output PROM, such as the CY7C245 or the CY7C261. The outputs will reach  $V_{CC}$  -Vt = 5V-1V = 4V. Each output will then require 4V/50 = 8 mA. Since there are eight outputs a total of 64 mA will be required.

Solving equation 6-1 for C yields;

$$C = I \frac{dt}{dV}.$$

(6-2)

The signal rise and fall times are 2 to 4 ns so we will use dt = 3 ns.

The last step is to assume a reasonable, tolerable droop in the capacitor voltage. Assume dV = 100 mV.

Therefore, substituting these values in equation 6-2 yields;  $(4 \times 10^{-3} \times 2 \times 10^{-9})$

$$C = \frac{64 \times 10^{-5} \times 5 \times 10^{-5}}{100 \times 10^{-3}} = 0.192 \times 10^{-9} = 192 \,\mathrm{pF}.$$

It is standard practice to use 0.01 to 0.1  $\mu$ F decoupling capacitors. A 0.01  $\mu$ F capacitor is capable of supplying 330 mA under the preceding conditions.

## Power Distribution (Continued)

Decoupling capacitors for high speed Cypress CMOS circuits should be of the high K ceramic type with a low ESR (Equivalent Series Resistance). Capacitors using 5 ZU dielectric are a good choice.

## Low Frequency Filter Capacitors

A solid tantalum capacitor of 10  $\mu F$  is recommended for each 50 to 100 ICs to reduce power supply ripple. This capacitor should be as close as possible to where the  $V_{CC}$  and ground enter the PCB or module.

## When Should Transmission Lines Be Terminated?

Transmission lines should be terminated when they are long. From the preceding analysis it should be apparent that

Long Line

$$> \frac{T_r}{2 T_{pd}}$$

Where T<sub>pd</sub> is the propagation delay per unit length.

For Cypress products, the rise time,  $T_{\rm r},$  is typically two nanoseconds.

The propagation delay per unit length has been shown to be as small as 1.7 ns per foot.

Long Line

$$> \frac{2 \text{ ns}}{2 \times 1.7 \text{ ns/ft.}} = 0.59 \text{ ft. or 7 inches.}$$

Not all lines exceeding 7 inches will need to be terminated. Terminations are usually only required on clock inputs, write and read strobe lines on SRAMs, and chip select or output enable lines on RAMs, PROMs, and PLDs. Address lines and data lines on RAMs and PROMs usually have time to settle.

In the case where multiple loads are connected to a transmission line, only one termination circuit is required. The termination network should be located at the load that is electrically the longest distance from the source. This is usually the load that is the longest physical distance from the source.

## **Types of Terminations**

There are three basic types of terminations. They are called series damping, parallel, and pullup/pulldown. Each has their advantages and disadvantages.

Except for series damping, the termination network should be attached to the input (load) that is electrically furthest away from the source. Component leads should be as short as possible in order to prevent reflections due to lead inductance.

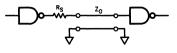

#### Series Damping

Series damping is accomplished by inserting a small resistor (typically  $10\Omega$  to  $75\Omega$ ) in series with the transmission line, as close to the source as possible, as illustrated in *Figure 8.1*. Series damping is a special case of damping in which the series resistor value plus the circuit output impedance is equal to the transmission line impedance. The strategy is to prevent the wave that is reflected back from the source by making the source reflection coefficient equal to zero.

The channel resistance (ON resistance) of the pulldown device for Cypress ICs is ten to twenty ohms (depending upon the current sinking requirements), so this value should be subtracted from the series damping resistor, R<sub>S</sub>.

Figure 8.1. Series Damping

0099-36

The disadvantage of the series damping technique is that during the two-way propagation delay time the voltage at the input to the line is half-way between the logic levels, due to the voltage divider action of Rs. This means that no inputs can be attached along the line, because they would respond incorrectly. However, any number of devices may be attached to the load end of the line because all of the reflections will be absorbed at the source.

Due to the low input current required by Cypress CMOS ICs, there will be essentially no DC power dissipation and the only AC power required will be to charge and discharge the parasitic capacitances.

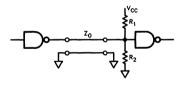

#### Pullup/Pulldown

The pullup/pulldown resistor termination shown in *Figure* 8.2 is included only for the sake of completeness. If both resistors are used there will be DC power dissipated all the time and if only a pulldown resistor is used DC power will be dissipated when the input is in the logic HIGH state. Due to these power dissipations, this termination is not recommended.

0099-37

Figure 8.2. Pullup/Pulldown

However, in special cases where inputs should be either pulled up (HIGH) for logic reasons or because of very slow rise and fall times, a pullup resistor to  $V_{CC}$  may be used in conjunction with the terminating network described below. DC power will be dissipated when the source is LOW.

### Parallel AC Termination; Figure 8.3

This is the recommended general purpose termination. It does not have the disavantage of the half-voltage levels of series damping and it causes no DC power dissipation. Loads may be attached anywhere along the line and they will see a full voltage swing.

Figure 8.3. Parallel AC

0099-38

## Types of Terminations (Continued)

The disadvantage is that it requires two components, versus the series damping termination of one. The value of the terminating resistor, R, should be slightly less than the line characteristic impedance.

#### Low Pass Filter Analysis

The parallel AC termination has a second advantage: it acts as a low-pass filter for short pulses.

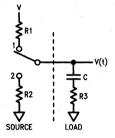

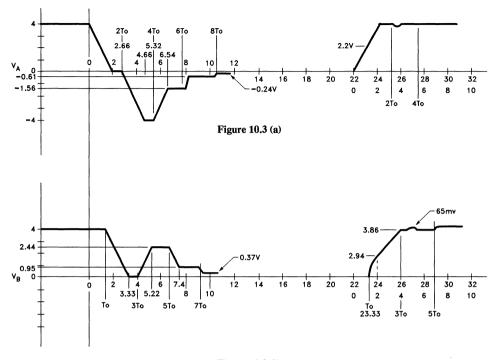

This can be verified by analysis of the response of the circuit, illustrated in *Figure 8.4*, to a positive and to a negative step function. The positive step function is generated by moving the switch from position 2 to position 1. The negative step function is generated by moving the switch from position 1 to position 2. The response of the circuit to a pulse is then the superposition of the two responses. The input impedance of the Cypress circuits that are connected to the termination network are so large that they may be ignored for this analysis.

Figure 8.4. Lumped Load

0099-43

Classic circuit analysis usually assumes an ideal (R1 = R2 = 0) source. In real-world digital circuits the source output impedance is not only non-zero, but also different depending upon whether the output is changing from LOW to HIGH or vice versa.

For Cypress integrated circuits,  $100\Omega > R1 > 30\Omega$  and  $20\Omega > R2 > 10\Omega$ , depending upon speed and output current sinking specifications.

#### **Positive Step Function Response**

The initial voltage on the capacitor is zero. At t = 0 the switch is moved from position 2 to position 1. At t = 0+ the capacitor appears as a short circuit and the voltage V is applied through R1 to charge the load (R3 C). The voltage between the capacitor and ground, V(t), is;

$$\mathbf{V}(\mathbf{t}) = \mathbf{V} \left(1 - \boldsymbol{\epsilon}^{\overline{(\mathbf{R}\mathbf{1} + \mathbf{R}\mathbf{3})\mathbf{C}}}\right)$$

(8-1)

In theory, the voltage across the capacitor reaches V when t equals infinity.

In practice, the voltage reaches 98% of V after 3.9 RC time constants. This can be verified by setting V(t)/V = 0.98 in equation 8-1 and solving for t.

#### **Negative Step Function Response**

The capacitor is charged to (approximately) V. At t = 0 the switch is moved from position 1 to position 2 and the capacitor is discharged. The voltage between the capacitor and ground, V(t), is;

$$V(t) = V \epsilon^{\frac{-t}{(R_2 + R_3)C}}$$

(8-2)

The voltage decays to 2% of its original value in 3.9 RC time constants. This can be verified by setting V(t)/V = 0.02 in equation 8-2 and solving for t.

#### First, the Ideal Case

Consider first the ideal case where R1 = R2 = 0. Let R3 = R in equations 8-1 and 8-2. If a positive pulse of width T is applied to the circuit of *Figure 8.4*, it will disappear if 4RC > T.

Because the discharge time constant is the same as the charging time constant for the ideal case, a negative going pulse of width T will also disappear if 4RC > T. i.e., if the applied signal were normally HIGH and went LOW, such as a write strobe on a SRAM, all negative glitches will be filtered out if they are less than 4RC time constants in width.

The maximum frequency that the circuit will pass is;

$$F(max.) = \frac{1}{2 T}.$$

(8-3)

This is true because the charging and discharging time constants are equal for the ideal case.

## Determination of the Capacitance, C, for the Ideal Case

The value of the capacitor, C, must be chosen to satisfy two conflicting requirements. First, it should be large enough to either absorb or supply the energy contained or removed when positive-going or negative-going glitches occur. Second, it should be small enough not to either delay the signal beyond some design limit or to slow the signal rise and fall times to greater (i.e., longer timewise) than 5 ns.

A third consideration is the impedance caused by the capacitive reactance, XC, of the capacitor. The digital waveforms applied to the AC termination can be expressed in terms of Fourier Series so that they can be manipulated mathematically. However, because these digital signals are not "periodic" in the classical meaning of the word, it is not clear that the "AC steady state analysis model" of XC is applicable.

In most applications, the degradation of the signal rise and fall times beyond 5 ns determines the maximum value of the capacitor. The procedure will be to calculate the rise-time between the 10% and 90% amplitude levels, equate this to 5 ns, and solve for C in terms of R.

## Types of Terminations (Continued)

Solving the equation V(t) = V (1 -

$$\epsilon^{\frac{-t}{RC}}$$

) for t yields;

t = R C ln  $\left[\frac{1}{1 - \frac{V(t)}{V}}\right]$

(8-4)

For

$$\frac{V(t)}{V} = 0.1$$

, t = 0.10 R C.

For  $\frac{V(t)}{V} = 0.9$ , t = 2.3 R C.

The time for the signal to transition from 10% to 90% of its final value is then T = 2.2 R C. Solving for C yields;

$$C = \frac{T}{2.2 R}$$

(8-5)

For T = 5 ns the following table may be constructed.

|                 | РСВ  | Wirewrap |

|-----------------|------|----------|

| $Z_{O}(\Omega)$ | 50   | 120      |

| R (Ω)           | 47   | 110      |

| C (max., pF)    | 48   | 20       |

| RC (ns)         | 2.25 | 2.2      |

| 4RC (ns)        | 9    | 8.8      |

What this table says is that  $50\Omega$  transmission lines on printed circuit boards that are terminated with RC networks should use a  $47\Omega$  resistor and a maximum capacitor of 48 pF. Under this condition, glitches of 9 ns or less will be eliminated. The second column applies to wirewrap construction.

### Then for the Real World

The value of R1 and R2 should be determined from the data sheet.

The value of R1 should be added to  $47\Omega$  and C then calculated using equation 8-5. Next, check to see that the charging RC time constant does not violate some minimum positive pulse width specification for the particular line. If so, reduce C.

Add the value of R2 to  $47\Omega$  and calculate C. Then check if the discharging RC time constant violates some minimum negative pulse width specification for the particular line. If so, reduce C.

## **Schottky Diode Termination**

In certain instances it may be expedient to use Schottky diodes to terminate lines. Where line impedances are not well defined, as in breadboards and backplanes, the use of diode terminations is convenient and may save time.

A typical diode termination is shown in Figure 9.1. The low forward voltage, V<sub>f</sub>, of the diode (typically 0.3 to 0.45V) clamps the input signal to a  $V_f$  below ground (lower diode) and  $V_{CC} + V_f$  (upper diode), thereby significantly reducing signal undershoot and overshoot. In some applications both diodes may not be required.

#### Figure 9.1. Schottky Diode Termination

0099-39

The advantages of diode terminations are:

- · Impedance matched lines are not required.

- The diodes replace terminating resistors or RC terminations.

- The clamping actions of the diodes reduce overshoot and undershoot.

- Although diodes are more expensive than resistors, the total cost of layout may be less because a precise, controlled transmission line environment is not required.

- If ringing is discovered to be a problem during system checkout the diodes can be easily added.

As with resistor or RC terminations, the leads should be as short as possible in order to avoid ringing due to lead inductance.

A few of the types of Schottky diodes commercially available are :

- 1N4148 (Switching)

- 1N5711

- MBD101 (Motorola)

- HP5042 (Hewlett Packard)

### **Example: Unterminated Line**

The following example is presented to illustrate the procedure for calculating the waveforms when a Cypress PLD is used to generate the write strobe for a Cypress SRAM. The PLD is a PAL®C 20 device and the SRAM is the CY7C189-25.

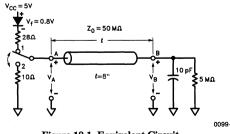

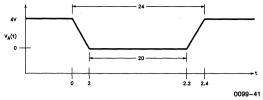

The equivalent circuit is illustrated in Figure 10.1 and the (unmodified) driving waveform in Figure 10.2. The rise and fall times are two nanoseconds. The length of the microstrip trace on the PCB is eight inches and the characteristic line impedance is 50 $\Omega$ . It is required to calculate the voltage waveforms at the source (point A) and the load (point B) as functions of time.

0099~40

#### Equivalent Circuits for The PLD and SRAM

The equivalent ON channel resistance of the PLD pullup device,  $28\Omega$ , was calculated using the output source current versus voltage graph over the region of interest (0 to 2V) from the data sheet. The equivalent resistance of the pulldown device,  $10\Omega$ , was calculated in a similar manner, using the output sink current versus output voltage graph, also on the data sheet.

The equivalent input circuit for the SRAM was constructed by approximating the input and stray capacitance with a 10 pF capacitor and the resistance with a 5 million ohm resistor. The input leakage current for all Cypress products is specified as a maximum of  $\pm 10 \ \mu$ A, which guarantees a minimum of 500,000 $\Omega$  at V<sub>in</sub> = 5V. Typical leakage current is one microampere.

#### **Transmission Line Calculations**

The next step is to calculate the propagation delay and loaded characteristic impedance of the line.

#### **Propagation Delay**

The unloaded propagation delay of the line is calculated using equation 5-3 with a dielectric constant of 5.

$$T_{pd} = 1.74 \text{ ns/ft.}$$

In order to calculate the loaded line propagation delay, the intrinsic capacitance must first be calculated using equation 2-5.

$$T_{pd} = Z_0 C_0$$

,

where  $Z_0$  is the intrinsic characteristic impedance and  $C_0$  is the intrinsic capacitance.

$$C_{O} = \frac{T_{pd}}{Z_{O}} = \frac{1.74 \text{ ns/ft.}}{50} = 34.8 \text{ }\rho\text{F/ft.}$$

The line is loaded with 10 pF, so equation 2-6 is used to compute the loaded propagation delay of the line.

$$T_{pd}' = T_{pd} \sqrt{1 + \frac{C_D}{C_O}}$$

$$T_{pd}' = 1.74 \text{ ns/ft.} \sqrt{1 + \frac{10 \text{ }\rho\text{F}}{34.8 \text{ }\rho\text{F/ft.} \times \frac{8 \text{ in.}}{12 \text{ in./ft.}}}}$$

$$T_{pd}' = 2.08 \text{ ns/ft.}$$

Note that the capacitance per unit length must be multiplied by the line length to arrive at an equivalent lumped capacitance.

#### **Characteristic Impedance**

2

The intrinsic line impedance is reduced by the same factor by which the propagation delay is increased (1.96). See equation 2-7.

$$Z_{\rm O}' = \frac{50\Omega}{1.196} = 41.8\Omega.$$

#### **Initial Conditions**

At time t = 0 the circuit of Figure 10.1 is in a quiescient state. The voltage at points A and B must be the same. By inspection;

$$\mathbf{VA} = \mathbf{VB} = (\mathbf{V}_{CC} - \mathbf{Vf}) \left(\frac{\mathbf{RL}}{\mathbf{RS} + \mathbf{RL}}\right)$$

$$= (5-1) \left(\frac{5 \times 10^{6}}{28 + 5 \times 10^{6}}\right) = 4\mathbf{V}$$

#### The Falling Edge of the Write Strobe

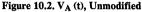

At t = 0 the driving waveform changes from 4V to 0V (approximately) with a fall time of two nanoseconds. This is represented in *Figure 10.1* by the switch arm moving from position 1 to position 2. The wave propagates to the load at the rate of 2 ns per foot (approximately) and arrives there

$$T_{O} = 2 \text{ ns/ft.} \times \frac{8 \text{ in.}}{12 \text{ in./ft.}} = 1.33 \text{ ns}$$

later, as illustrated in Figure 10.3 (b).

The reflection coefficient at the load is  $\rho L = 1$ , so a nearly equal and opposite polarity waveform is propagated back to the source from the load, arriving at  $t = 2 T_O = 2.66$  ns, as shown in *Figure 10.3 (a)*. (See Table 3 {h}). Note that the falltime is preserved. The reflection coefficient at the source is;

$$\rho_{\rm S} = \frac{\rm RS - Z_{\rm O}'}{\rm RS + Z_{\rm O}'} = \frac{10 - 41.8}{10 + 41.8} = -0.61$$

The magnitude of the reflected voltage at the source is then;

$$VS1 = -4V \times (-0.61) = 2.44V.$$

This wave propagates from the source to the load and arrives at  $t = 3 T_0$ , and adds to the (zero volts) signal. The risetime is preserved, so the time required for the signal to go from 0V to 2.44V is;

$$t_r = 2.44V \times 2 \text{ ns}/4V = 1.22 \text{ ns}.$$

The signal at the load thus reaches the 2.44V level at time  $t = 3 T_O + 1.22 ns = 5.22 ns$  and remains at that level until the next reflection occurs at  $t = 5 T_O$ . The wave that arrived at the load at 3 T<sub>O</sub> is reflected back to the source and arrives at  $t = 4 T_O (5.32 ns)$ . The 2.44V level adds to the -4V level, so that the resultant level is -1.56V. The risetime is preserved, so that this level is reached at  $t = 4 T_O + 1.22 ns = 6.54 ns$ , and maintained until the next reflection occurs at  $t = 4 T_O$  is reflected back to the load and arrives at  $t = 5 T_O$ . The portion that is reflected back is;

$$VS2 = 2.44 \times (-0.61) = -1.49V$$

.

Figure 10.3 (b)

This subtracts from the 2.44V level to give 2.44 - 1.49 = 0.95V. The falltime is preserved, so the time required for the signal to go from 2.44V to 0.95V is;

$$t_f = 1.49V \times 2 \text{ ns}/4V = 0.75 \text{ ns}.$$

The 0.95V level is thus reached at time t = 5  $T_{\rm O}$  + 0.75 ns = 7.4 ns.

At t = 6 T<sub>O</sub> the 0.95V wave arrives back at the source, where it subtracts from the -1.56V level to give -0.61V. The risetime is t<sub>r</sub> = 0.95  $\times$  0.5 ns/V = 0.45 ns.

The 0.95V wave that arrived at the source at  $t = 6 T_0$  is reflected back to the load and arrives at  $t = 7 T_0$ . The portion that is reflected back is;

ν

$$S_3 = 0.95 \times (-0.61) = -0.58V.$$

This subtracts from the 0.95V level to give 0.37V. The falltime is approximately 0.5 ns.

This process continues until the voltages at points A and B decay to approximately zero volts.

## **Observations**

The positive reflection coefficient at the load and the negative reflection coefficient at the source result in an oscillatory behavior that eventually decays to acceptable levels. The voltage at point A reaches -0.61V after 6 T<sub>O</sub> delays and the voltage at point B reaches 0.37V after 7 T<sub>O</sub> delays.

0099-42

The reflection at the load that causes the voltage to exceed the TTL minimum ONE level (2V) at  $T = 3 T_O$  could cause a problem if either the data to be written in the RAM changes up to 5 T<sub>O</sub> delays after the falling edge of the write strobe or if the observed shortening of the write strobe by 5 T<sub>O</sub> delays violates the minimum write strobe specification.

However, if this reflection occurred on a clock line to a logic device, registered PROM, or a PLD the reflection could be interpreted by the device as a second clock. The width of the pulse caused by the reflection in this case is  $2 T_O = 2.66$  ns, which is probably too short to be detected. If the line were either slightly longer or more heavily

capacitively loaded the pulse would be wider and could be detected as a second clock.

#### The Rising Edge of the Write Strobe

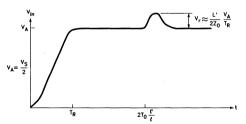

At t = 22 ns the rising edge of the write strobe begins, which is the equivalent of closing the switch in *Figure 10.1* in the 1 position. For this analysis it its convenient to start the time scale over at zero, as is shown in *Figures 10.3 a* and b.

If the forcing function were a step function, the equations of Table 1 (h) would apply. The time constant in the equation is:

$$T = \frac{R Z_{O'} Ce}{R + Z_{O'}}.$$

(10-1)

Because  $R \gg Z_O', T = Z_O'$  Ce, where  $Z_O' = 41.8\Omega$  and Ce = 33.2  $\rho F.$

This is the equivalent of saying that the five megohm device input resistance can be ignored for transient circuit analysis. Substitution of  $Z_{O}'$  and Ce into the preceding equation yields a time constant of T = 1.39 ns.

Writing the equation for the voltages for the circuit of Figure 10.1

$$VA(t) = i Z_{O'} + \frac{1}{Ce} \int_{0}^{t} i dt.$$

(10-2)

Also, VA(t) = Kt U(t) - K(t - T1) U(t - T1). (10-3)

Where Kt is the rising edge of the write strobe (K = 2V/ns) applied at t = 0 using a unit step function, U(t), and -K (t -T1) represents an equal but opposite waveform applied at t = T1 (after the risetime) using a unit step function, U(t -T1).

Equating the equations and taking the LaPlace transforms of both sides yields:

$$\frac{K}{s^2} - \frac{K \epsilon^{-T1S}}{s^2} = Z_{O'} I(s) + \frac{I(s)}{Ce s} = \left(Z_{O'} + \frac{1}{Ce s}\right) I(s).$$

(10-4)

However,

$$VB(t) = \frac{1}{Ce} \int_{0}^{t} i dt$$

, or  $VB(s) = \frac{I(s)}{Ce s}$ .

Therefore:

$$\frac{\mathbf{K}}{\mathbf{s}^2} - \frac{\mathbf{K} \ \boldsymbol{\epsilon}^{-\text{T1S}}}{\mathbf{s}^2} = \left( \mathbf{Z}_{\mathbf{O}'} + \frac{1}{\text{Ce S}} \right) \text{Ce s VB(s).} \quad (10\text{-}5)$$

Solving for VB(s) yields:

$$VB(s) = \frac{\frac{K}{s^2} \left(1 - e^{-T1S}\right)}{Ce s \left(Z_{O'} + \frac{1}{Ce s}\right)}.$$

(10-6)

Which is equivalent to:

$$VB(s) = \frac{\frac{K}{Z_{O'}Ce}(1 - e^{-TIS})}{s^{2}\left(S + \frac{1}{Z_{O'}Ce}\right)}.$$

(10-7)

Taking the inverse LaPlace transform yields:

$$VB(t) = \left[K Z_{O}' Ce\left(\epsilon^{\frac{-t}{Z_{O}' Ce}} - 1\right) + Kt\right]U(t) -$$

(10-8)

$$\left[K Z_{O}' Ce\left(\epsilon^{\frac{-(t-T1)}{Z_{O}' Ce}} - 1\right) + K(t-T1)\right]U(t-T1)$$

Equation 10-8 consists of two terms. The first term applies from time zero up to and including T1 and the second term applies after T1.

$$VB(t) = \frac{K Z_{O}' Ce}{T1} \left( \epsilon^{\frac{-t}{Z_{O}' Ce}} - 1 \right) + \frac{K}{T1}(t) t \le T1 \quad (10-9)$$

$$VB(t) = \frac{K Z_0' Ce}{T1} (1 - \epsilon^{\frac{T1}{Z_0' Ce}}) \epsilon^{\frac{-t}{Z_0' Ce}} + K1 t > T1 (10-10)$$

where K1 = final value = 4V

L

Substitution of the proper values into equation 10-9 yields at t = T1 = 2 ns.

VB (t = T1) =

$$\frac{2 \times 41.8 \times 33.2 \times 10^{-12}}{2 \times 10^{-9}} (\epsilon^{-1.439} - 1) + \frac{2V}{ns} \times 2 \text{ ns}$$

$$= -1.057 + 4 = 2.94V$$

If the forcing function would have been a step function the equation would be:

$$VB(t) = 4V (1 - \epsilon^{\frac{-t}{Z_0' Ce}})$$

(10-11)

at t = 2 ns, VB = 3V, which is greater than the 2.94V calculated using equation 10-9.

At  $t = (22 \text{ ns}) + T_0$  the voltage waveform begins to build up at the load and continues to build until the first reflection from the source occurs at  $t = 3 T_0$ .

Equation 10-10 is used to calculate the voltage at the load at  $t = 2 T_O$  (because 1  $T_O$  is used for propagation delay time).

$$VB(t = 2 T_0) =$$

$$\frac{-2V \times 41.8 \times 33.2 \times 10^{-12}}{2 \times 10^{-9}} (1 - \epsilon^{-1.439}) (\epsilon^{-2}) + 4$$

= -1.39 (0.762) (0.135) + 4

= -0.143 + 4 = 3.86V

The voltage at the load will remain at this value until the first reflection from the source reaches the load at t = 3  $T_{O}$ .

Meanwhile, at  $t = T_0$ , the wave at the load is reflected back to the source and arrives there at  $t = 2 T_0$ . It subtracts from the 4V level at the source as illustrated in Table 4 (c). The amplitude of the "droop" is given by:

$$V_{\rm r} \simeq \frac{{\rm C}' \, {\rm Z}_{\rm O}'}{2} \frac{{\rm V}_{\rm O}}{{\rm TR}} \tag{10-11}$$

for the case Vs = ZO'.

If  $V_S \neq Z_{O'}$  equation 10-11 must be modified. Instead of  $\frac{V_O}{2}$  the voltage is  $V_O\left(\frac{R_S}{R_S + Z_{O'}}\right)$ , so that equation 10-11 becomes:

$$V_{r} \approx \frac{C' Z_{O}' V_{O}}{TR} \left(\frac{R_{S}}{R_{S} + Z_{O}'}\right). \quad (10-12)$$

where: C' = 10 pF

$$Z_{O}' = 41.8\Omega$$

$$R_{S} = 28\Omega$$

$$T_{\rm P} = 2 \, \rm ns$$

$$V_0 = 4V$$

Substitution of these values into equation 10-12 yields:

$$V_{r} = 0.33V.$$

4V - 0.33V = 3.67V, so there is no danger of the voltage dropping below the minimum HIGH level.

The reflection coefficient at the source is:

$$\rho s = \frac{R_S - Z_O'}{R_S + Z_O'} \text{ where: } \begin{array}{l} R_S = 28\Omega \\ Z_O' = 41.8\Omega \\ \rho s = -0.198 \end{array}$$

The amount of voltage reflected from the source back to the load is then:

$$VS_1 = (-0.33) \times (-0.198) = +0.065V_1$$

This same result could have been obtained by applying the ramp function of *Figure 10.2* to a large resistor and then to a capacitive load and adding the results using superposition.

#### Observations

The risetime of the waveform at the load is reduced by the 10 pF load capacitor. The reflection at the source caused by the load capacitor is insufficient to reduce the 4V level to less than the TTL one level (2V).

The reflection coefficient at the source is sufficiently small so that the energy reflected back to the load is insufficient to cause a problem.

#### Summary

The example has demonstrated that, under certain conditions, the voltage reflections caused by the impedance mismatch between a PCB trace and the input of a Cypress CMOS integrated circuit may cause a pulse whose energy is sufficient to be detected by another circuit.

It is the responsibility of the system designer to identify and to analyze these conditions and to then modify the design such that the reflections will not occur.

#### References

- 1. Matick, Richard E.: Transmission Lines For Digital and Communications Networks, McGraw Hill, 1969.

- Blood, Jr, William R.,: MECL System Design Handbook, Motorola Inc., 1983.

**NOTES:**

## Power Characteristics of Cypress Products

## Introduction

## SCOPE AND PURPOSE

This document presents and analyzes the power dissipation characteristics of Cypress products. The purpose of this document is to provide the user with the knowledge and the tools to manage power when using Cypress CMOS products.

## **DESIGN PHILOSOPHY**

The design philosophy for all Cypress products is to achieve superior performance at reasonable power dissipation levels. The CMOS technology, the circuit design techniques, architecture and the topology have been carefully combined in order to optimize the speed/power ratio.

## SOURCES OF POWER DISSIPATION

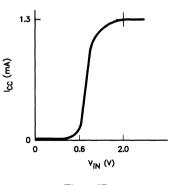

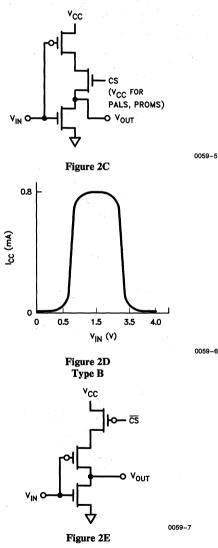

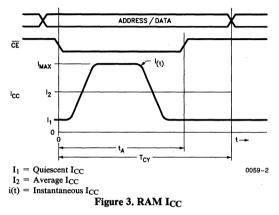

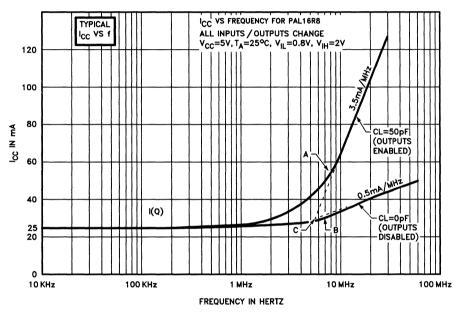

Power is dissipated within the integrated circuit as well as external to it. Both internal and external power have a quiescent (or DC) component and a frequency dependent component. The relative magnitudes of each depend upon the circuit design objectives. In circuits designed to minimize power dissipation at low to moderate performance, the internal frequency dependent component is significantly greater than the DC component. In the high performance circuits designed and manufactured by Cypress, the internal frequency dependent power component is much less than the DC component. The reason for this is that a large percentage of the internal power is dissipated in linear circuits such as sense amplifiers, bias generators and voltage/current references that are required for high performance.

#### **External Power Dissipation**

The input impedance of CMOS circuits is extremely high. As a result, the DC input current is essentially zero ( $10 \,\mu A$  or less). When CMOS circuits drive other CMOS circuits there is practically no DC output current. However, when CMOS circuits drive either bipolar circuits or DC loads, external DC power is dissipated. It is standard practice in the semiconductor industry to NOT include the current from a DC load in the device  $I_{CC}$  specification. Cypress supports this practice. It is also standard practice to NOT include the current required to charge and discharge capacitive loads in the data sheet  $I_{CC}$  specification. Cypress also supports this standard practice.

#### **Frequency Dependent Power**

CMOS integrated circuits inherently dissipate significantly less power than either bipolar or NMOS circuits. In the ideal digital CMOS circuit there is no direct current path between  $V_{CC}$  and  $V_{SS}$ ; in circuits using other technologies such paths exist and DC power is dissipated while the device is in a static state.

The principal component of power dissipation in a poweroptimized CMOS circuit is the transient power required to charge and discharge the capacitances associated with the inputs, outputs, and internal nodes. This component is commonly called  $CV^{2}f$  power and is directly proportional to the operating frequency, f. The corresponding current is given by the formula

#### $I_{CC}(f) = CVf.$

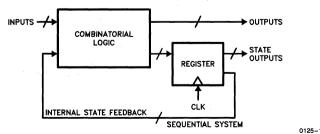

The primary sources of frequency dependent power are due to the capacitances associated with the internal nodes and the output pins. For "regular" logic structures, such as RAMs, PROMs and FIFOs the internal capacitances are "balanced" so that the same delay and, therefore, the same frequency dependent power is dissipated independent of the location that is addressed. This is not true for programmable devices such as PALs because the capacitive loading of the internal nodes is a function of the logic implemented by the device. In addition, PALs and other types of logic devices may contain sequential circuits so the input frequency and the output frequency may be different.

The capacitance of each input pin is typically 5 pF, so its contribution to the total power is usually insignificant.

#### Note:

The Cypress Power/Speed Program, which implements the equations in this application note, is available from Cypress for your use on personal computers.

PAL® is a registered trademark of Monolithic Memories.

## Introduction (Continued)

#### **Derivation of Applicable Equations**

The charge, Q, stored on a capacitor, C, that is charged to a voltage, V, is given by the equation;

$$Q = CV. \qquad EQ.1$$

Dividing both sides of equation 1 by the time required to charge and discharge the capacitor (one period or T) yields;

$$\frac{Q}{T} = \frac{CV}{T} \qquad EQ.2$$

By definition, current (I) is the charge per unit time and

$$f = \frac{1}{T}$$

Therefore,

$$I = CVf. \qquad EQ.3$$

The power (P = VI) required to charge and discharge the capacitor is obtained by multiplying both sides of equation 3 by V.

$$\mathbf{P} = \mathbf{V}\mathbf{I} = \mathbf{C}\mathbf{V}^2\mathbf{f} \qquad \mathbf{E}\mathbf{Q}.\mathbf{4}$$

It is standard practice to make the assumption that the capacitor is charged to the supply voltage ( $V_{CC}$ ) so that

$$\mathbf{P} = \mathbf{V}_{\mathbf{CC}}\mathbf{I} = \mathbf{C} \, [\mathbf{V}_{\mathbf{CC}}]^2 \mathbf{f} \qquad \mathbf{EQ. 5}$$

The total power consumption for a CMOS integrated circuit is dependent upon:

- the static (quiescent or DC) power consumption.

- the internal frequency of operation

- the internal equivalent (device) capacitance

- the number of inputs, their associated capacitance, and the frequency at which they are changing

• the number of outputs, their associated capacitance, and the frequency at which they are changing

In equation form:

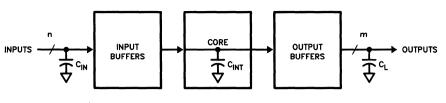

$$P_{D} = [(C_{IN}) (F_{IN}) + (C_{INT}) (F_{INT}) + (C_{LOAD}) (F_{LOAD})]$$

$$[V_{CC}]^2 + I_{CC} (quiescent) V_{CC}. \qquad EQ. 6$$

The first three terms are frequency dependent and the last is not. This equation can be used to describe the power dissipation of every IC in the system. The total system power dissipation is then the algebraic sum of the individual components.

The relative magnitudes of the various terms in the equation are device dependent. Note that equation 6 must be modified if all of the inputs, internal nodes or all of the outputs are not switching at the same frequency. In the general case, each of the terms is of the form C1 F1 + C2 F2 + C3 F3 + ... Cn Fn. In practical reality the terms are estimated using an equivalent capacitance and frequency.

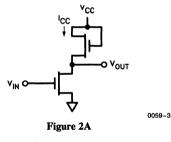

#### **Transient Power: Input Buffers and Internal**

In the N-well CMOS inverter, the P-channel pullup transistor and the N-channel pulldown transistor (which are in series with each other between  $V_{CC}$  and  $V_{SS}$ ) are never on

at the same time. This means that there is no direct current path between  $V_{CC}$  and ground, so that the quiescent power is very nearly zero. In the real world, when the input signal makes the transition through the linear region (i.e., between logic levels) both the N-channel and the P-channel transistors are partially turned ON. This creates a low impedance path between  $V_{CC}$  and  $V_{SS}$ , whose resistance is the sum of the N-channel and P-channel resistances. These gates are used internally in Cypress products.

#### DC or Static Power

In addition to the conventional gates there are sense amplifiers, input buffers and output buffers, bias generators and reference generators that all dissipate power. The RAMs and FIFOs also have memory cells that dissipate standby power whether the IC is selected or not. The PROM and PAL® products have EPROM memory cells that do not dissipate as much standby power as a RAM cell.

#### **Power Down Options**

Many of the Cypress static RAMs have power down options that enable the user to reduce the power dissipation of these devices by approximately an order of magnitude when they are not accessed. The technique used is to disable or turn-off the input buffers and the sense amplifiers.

#### Worst Case Device Power Specifications